Fault Tree Analysis (FTA) stands as a pivotal methodology in assessing and mitigating risks across industries, from aerospace to software engineering. Being a top-down, deductive technique, Fault Tree Analysis (FTA) dissects a system’s pathways to locate potential flaws, ensuring the probability of failure remains manageable. At the helm of this analytical process are fault tree analysis symbols, fundamental tools that unravel complex failure paths into understandable and actionable insights.

Role of Fault Tree Analysis Symbols

Fault Tree Analysis symbols act as the language through which systems articulate possible failure points. They simplify the visualization of event interactions, and their standardized nature ensures that these diagrams are universally comprehensible, fostering collaboration across diverse sectors. This standardization of fault tree analysis symbols becomes particularly advantageous when teams from various technical backgrounds collaborate on troubleshooting and system improvement efforts.

These fault tree analysis symbols, comprising logic gates and event markers, play a crucial role in forming the scaffolding onto which risk analyses are constructed. Logic gates like AND, OR, and NOT define the relationships between events, while different event symbols specify the nature and origin of faults within the system. As a result,a simple fault tree analysis example example effectively translates the cascading effects of component failures into actionable strategies for system enhancement.

Utilizing tools like Creately, professionals can further enhance their diagramming capabilities. Creately offers a visual workspace that supports creating intricate FTA diagrams, thus empowering project managers and engineers to design better systems and engage in collaborative troubleshooting. By capturing requirements and ideas visually, these tools ensure efficient fault analysis and optimize organizational workflows. With such capabilities, industry professionals are well-equipped to analyze and rectify system shortcomings.

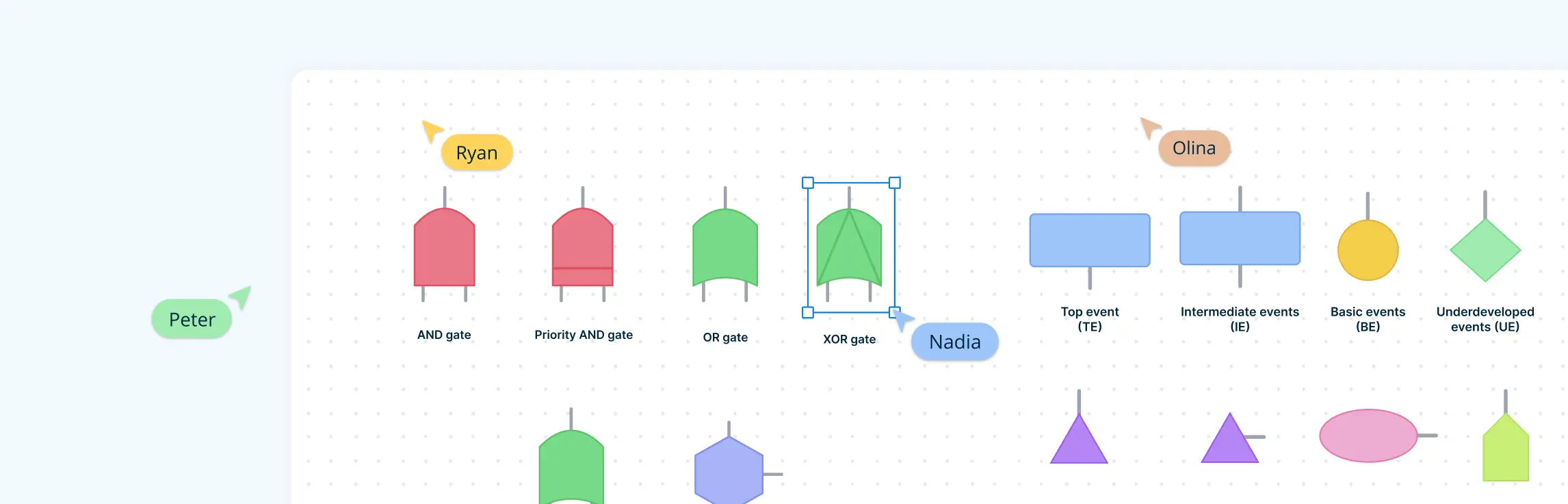

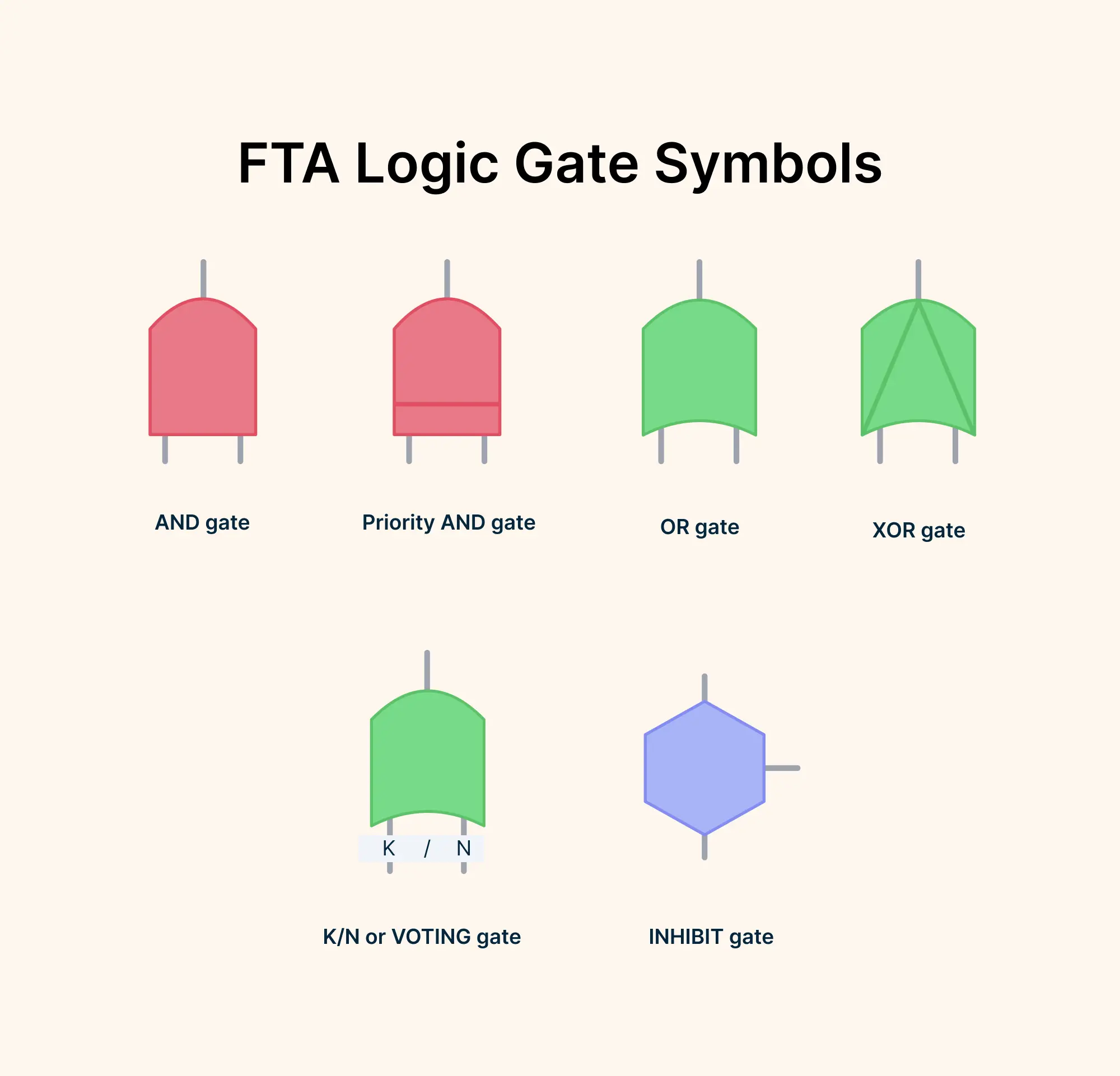

Logic Gates in Fault Tree Analysis Symbols

Logic gate symbols are fundamental in Fault Tree Analysis (FTA), providing the structure and clarity necessary to assess potential faults in complex systems. These fault tree analysis symbols simplify intricate systems into manageable diagrams, allowing engineers and analysts to evaluate risks and failure scenarios effectively. Below are the primary types of logic gates commonly used in FTA, each serving a specific function in the fault analysis process.

AND Gate

The AND gate symbol represents a situation where the output event occurs only if all input events occur. This gate is essential when multiple conditions must be true simultaneously for a fault to happen. For example, in system reliability, the output (system failure) will occur only if all the components (input events) fail. It highlights the need for complete failure across all contributing components to result in a system-wide malfunction.

| Input 1 | Input 2 | Output |

| T | T | T |

| T | F | F |

| F | T | F |

| F | F | F |

OR Gate

An OR gate symbol indicates that the output event will happen if at least one of the input events occurs. This is particularly important in systems where a fault could be triggered by any one of several independent failures. The OR gate demonstrates that even if only one component fails, it can cause a system failure, making it an ideal representation of scenarios where multiple failure pathways can lead to the same outcome.

| Input 1 | Input 2 | Output |

| T | T | T |

| T | F | T |

| F | T | T |

| F | F | F |

Exclusive OR Gate

The Exclusive OR (XOR) gate operates on the principle of “any but not all.” The output event occurs only when exactly one of the input conditions is met, but not when all conditions are satisfied. This gate is useful in systems where only one failure among several is required to cause a fault, but not all failures are needed to trigger the event.

| Input 1 | Input 2 | Output |

| T | T | F |

| T | F | T |

| F | T | T |

| F | F | F |

Priority AND Gate

A Priority AND gate specifies that the output will occur only after several input events occur in a defined sequence. This gate is used in situations where specific ordering or timing of failures is critical to the system’s malfunction, emphasizing the importance of sequence in the failure process.

| Input 1 | Input 2 | Output |

| T, occurred first | T, occurred second | T |

| T, occurred second | T, occurred first | F |

| T | F | F |

| F | T | F |

| F | F | F |

Inhibit Gate

An Inhibit gate is a specialized form of an AND gate. In this gate, the output event will occur only if all input events happen and an additional conditional event also takes place. This gate is used to model situations where a fault depends not only on multiple failures but also on a specific external condition, such as a failure in one component being dependent on the activation of another event.

| Input 1 | Input 2 | Conditioning Event | Output |

| T | T | T | T |

| T | T | F | F |

| T | F | T | F |

| T | F | F | F |

| F | T | T | F |

| F | T | F | F |

| F | F | T | F |

| F | F | F | F |

Voting Gate

A voting gate is used when the output occurs, but only if a certain number of inputs happen. It is represented by a symbol that indicates the required number of inputs out of the total available inputs (e.g., 2:3, meaning 2 of the 3 inputs must occur). Voting gates are valuable in redundancy systems where multiple independent failures may be necessary to cause a system failure. When the required number of inputs equals one, the voting gate behaves like an OR gate; when it equals the total number of inputs, it functions like an AND gate.

| Input 1 | Input 2 | Input 3 | Output |

| T | T | T | T |

| T | T | F | T |

| T | F | T | T |

| T | F | F | F |

| F | T | T | T |

| F | T | F | F |

| F | F | T | F |

| F | F | F | F |

These logic gates—AND, OR, XOR, Priority AND, Inhibit, and Voting—are essential for constructing detailed fault trees that represent complex systems and help assess their reliability and safety. By accurately mapping these gates within a fault tree, engineers can predict system failures more effectively, ensuring better preparedness and mitigation strategies across various industries.

Application of Logic Gates in Risk Analysis

Logic gates in FTA are pivotal in executing risk analysis and system reliability evaluations. By facilitating the breakdown of complex failure mechanisms into simpler components, these gates offer a deep dive into system dynamics. The application of these fault tree analysis symbols allows organizations to preemptively identify potential fault combinations that might lead to system failures.

Industries like aerospace or nuclear engineering benefit significantly from the structured approach provided by FTA and logic gate symbols. This methodical perspective aids in enforcing stringent reliability standards and fortifying systems against potential disruptions. With the help of Logic Diagram Maker, professionals can simulate intricate network circuits effectively, ensuring that their analyses are both comprehensive and actionable.

Furthermore, collaboration plays a critical role in optimizing FTA through shared insights and collectively addressing challenges in project workspaces. By employing collaborative troubleshooting frameworks, such as Creately’s visual workspace, teams can integrate real-time improvements and troubleshoot potential faults collaboratively. This streamlined approach supports seamless communication and problem resolution, bolstering incident management and enhancing the overall integrity of fault tree analysis.

Harnessing logic gates in fault trees not only clarifies the propagation of faults but also assists in strategizing effective prevention measures. As fault tree analysis symbols evolve alongside technological advancements, their role becomes increasingly sophisticated, embedding themselves deeper into the strategic toolkit used for designing resilient systems.

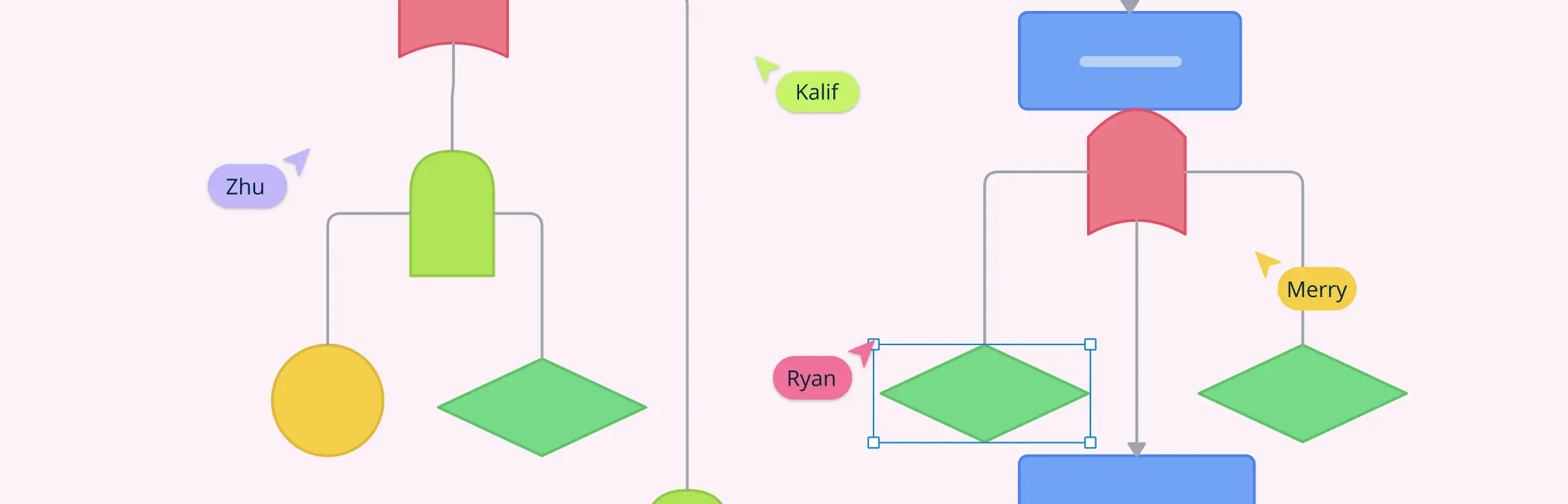

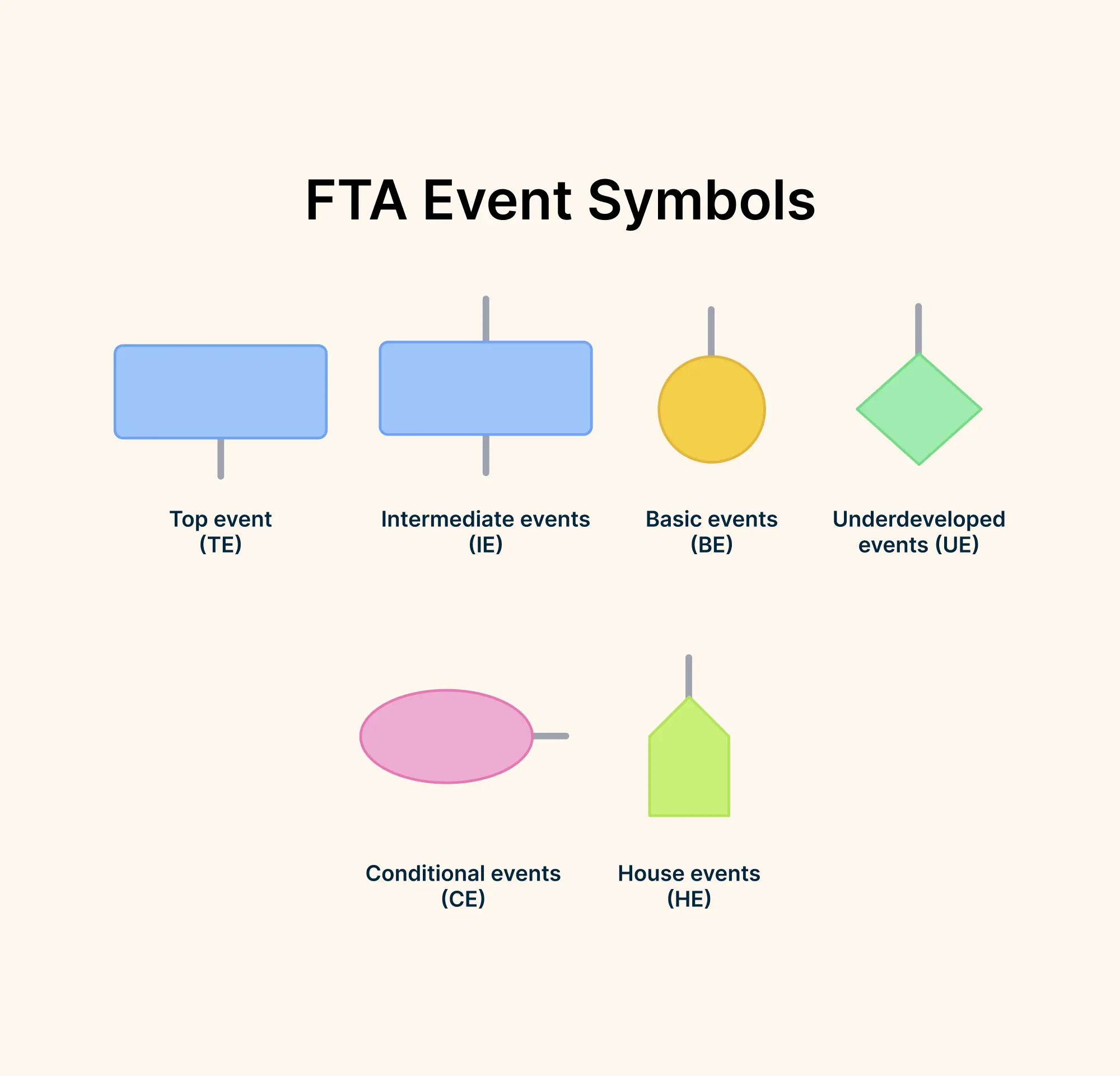

Event Types and Their Fault Tree Analysis Symbols

This section explores the various event types and their corresponding fault tree analysis symbols. Each event type plays a unique role in constructing fault tree diagrams, helping analysts visualize and understand the pathways leading to system failures. From basic events that pinpoint root causes to advanced fault tree analysis symbols like house and conditioning events that add depth and flexibility, these elements are crucial for a comprehensive analysis. Understanding these fault tree analysis symbols ensures accurate modeling and more effective risk management.

Top Event (TE)

The top event is the focal point of fault tree analysis. It represents the primary system failure or undesirable event that prompts the analysis. Unlike other events in the fault tree, the top event has no outputs, as it signifies the starting point of the failure investigation.

Top events provide the framework for the entire fault tree, guiding the analysis toward understanding the pathways and conditions that lead to this critical failure. By identifying and defining the top event, analysts can systematically break down the fault tree to uncover contributing factors and calculate the probability of system failure.

Intermediate Events (IE)

Intermediate events occur between the top event and basic events, representing failures caused by one or more preceding events. These events serve as both inputs and outputs in the fault tree, connecting different levels of analysis.

An intermediate event may result from a combination of basic or other intermediate events and can lead to further failures downstream. By analyzing intermediate events, fault tree analysts can identify potential failure chains and evaluate how different system components interact to contribute to the top event. This level of detail is crucial for pinpointing vulnerabilities and implementing corrective measures.

Basic Events (BE)

Basic events are the foundational components in fault tree analysis, representing root causes such as hardware failures, human errors, or software issues. These events terminate a fault tree branch, meaning no further breakdown is possible. They are crucial for calculating failure probabilities, which propagate through the tree to determine the likelihood of higher-level events. Basic events provide the starting point for understanding and mitigating system risks.

Underdeveloped Events (UE)

Undeveloped events, also known as underdeveloped events, represent the lowest level of detail within a fault tree, similar to basic events. However, they differ in one key aspect: undeveloped events indicate that further breakdown or refinement is possible but has not been pursued. This could be due to several reasons, such as the event’s minimal impact on the overall analysis or the unavailability of sufficient data at the time.

These events often serve as placeholders, signaling areas where future investigation may be warranted. For instance, in some cases, an undeveloped event might represent a component failure for which detailed failure data is not yet available. Alternatively, it could mark a low-priority event that doesn’t significantly influence the system’s top-level failure probability.

By including undeveloped events, analysts acknowledge gaps in their analysis while maintaining the integrity of the fault tree. This transparency ensures that stakeholders are aware of potential areas for improvement without compromising the current study’s objectives.

Conditioning Events (CE)

Conditioning events are specialized fault tree analysis symbols used to impose specific conditions on the operation of Inhibit gates. These events define prerequisites that must be met for the gate to allow fault propagation. For example, a conditioning event could represent an operational mode or environmental condition that restricts system behavior.

By using conditioning events, analysts can model scenarios where failures depend on external factors or constraints. This adds a layer of specificity, ensuring the fault tree accurately reflects real-world conditions and enhances the precision of the analysis. Conditioning events are particularly useful in systems where certain faults are only relevant under specific circumstances.

House Events (HE)

House events are a unique type of fault tree analysis symbols. House events provide a mechanism for toggling parts of the fault tree on or off. Assigning a probability of 0 to a house event excludes that event from the analysis, while a probability of 1 includes it. This capability is essential for exploring various scenarios, such as testing the impact of specific failures or operational changes on the overall system.

House events streamline fault tree analyses by allowing sections of the diagram to be dynamically adjusted without needing to redraw or modify the entire tree. This flexibility is especially beneficial in iterative analyses, where different configurations or conditions are explored to evaluate system resilience.

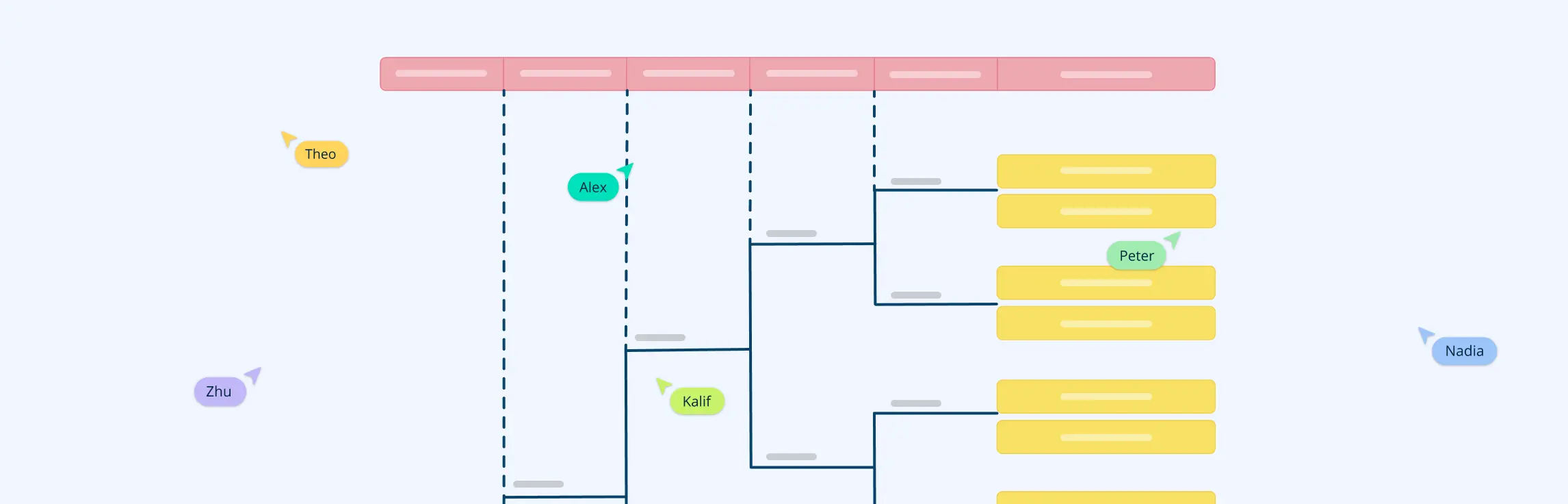

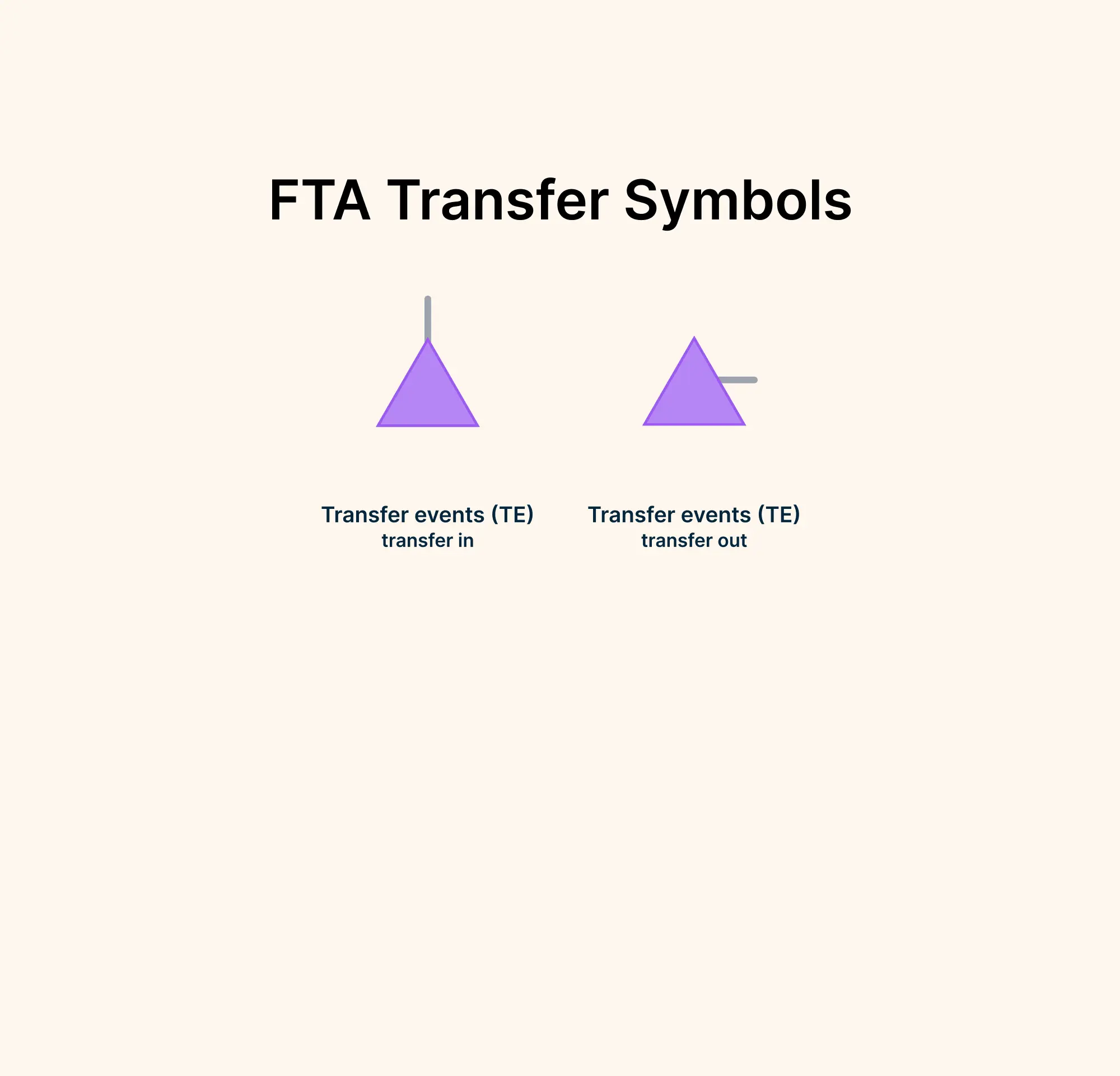

The Role of Transfer Symbols

In Fault Tree Analysis (FTA), transfer symbols are essential for maintaining organization and clarity, especially in large and complex systems. These fault tree analysis symbols allow analysts to connect different sections of a fault tree when the diagram becomes too large to fit on a single page or screen. Instead of crowding the diagram, these fault tree analysis symbols create links that guide the analysis across separate sections, enabling a comprehensive view of the fault pathways without overwhelming the visual space.

Transfer symbols come in two types: Transfer-out and Transfer-in events.

- Transfer-out events are represented by a triangle with an output pointing to the right, indicating that part of the fault tree is being transferred to another section.

- Transfer-in events are symbolized by a triangle with an input at the top, showing where the transferred section re-enters the fault tree.

These transfer events enable analysts to split a large fault tree into manageable parts, which can then be analyzed individually and connected seamlessly. This method simplifies the process of mapping fault scenarios, ensuring that the larger, more intricate systems are still comprehensively examined without losing critical information in the analysis.

Best Practices for FTA Diagramming

- Start with a Clear Objective: Begin by defining the top undesired event that needs analysis. Understanding the ultimate goal guides the entire diagramming process.

- Comprehensive System Understanding: Before constructing the diagram, ensure a thorough grasp of the system’s components and their interconnections. This understanding facilitates accurate representation and analysis of potential failure points.

- Utilize Standardized FTA Symbols: Utilize standardized fault tree analysis symbols to maintain clarity and consistency, enabling effective communication across teams. Fault tree analysis symbols like logic gates and transfer symbols are instrumental in depicting logical relationships and connections within the system.

- Iterative Development and Evaluation: Develop the fault tree iteratively, evaluating each branch for possible simplifications. This step refines the diagram and enhances its reliability in highlighting critical failure paths.

- Collaborative Engagement: Engage cross-functional teams to gain diverse insights during the analysis phase. Including various perspectives enriches fault tree accuracy and improves system robustness.

- Employ Advanced Tools: Leveraging tools like Creately enhances diagramming capabilities through visual collaboration, ensuring high-quality and efficient analysis processes.

Helpful Resources

Evaluate the reliability, maintainability and safety of systems faster with this easy-to-use visual tool.

Dive into the fundamentals of fault tree analysis with this guide. Discover effective techniques, proven practices, and how it enables industries to enhance safety and reliability.

Learn about innovative problem-solving strategies and simplifying complex challenges through organized visualization.

Why You Should Use Creately for Fault Tree Analysis

Fault Tree Analysis is a critical tool for assessing system reliability, identifying potential failure points, and ensuring safety in complex systems. While FTA can be a highly detailed and intricate process, Creately simplifies and enhances the entire fault tree analysis workflow, making it a powerful tool for engineers, safety professionals, and teams working on risk assessment and system reliability.

Here’s why Creately is the ideal platform for performing Fault Tree Analysis:

1. User-Friendly Interface for Building Fault Trees

Creately offers an intuitive, drag-and-drop interface that allows you to quickly build and customize fault tree diagrams. Whether you are a seasoned FTA expert or new to fault tree analysis, Creately makes it easy to organize and map out complex failure scenarios. With an extensive library of fault tree analysis symbols, including event types and logic gates, you can create precise diagrams without needing advanced technical skills or specialized software knowledge.

2. Collaborative Real-Time Editing

In today’s fast-paced and interconnected work environments, collaboration is key. Creately supports real-time collaboration, allowing multiple team members to work together on the same fault tree diagram simultaneously, regardless of location. This collaborative feature ensures that all stakeholders—whether engineers, risk analysts, or managers—can contribute to the analysis, provide feedback, and make updates instantly.

- Real-time comments and annotations make communication seamless, ensuring everyone is on the same page.

- Version control ensures that no data is lost, and team members can track changes made over time.

3. Comprehensive Symbol Library

Creately includes a comprehensive library of fault tree analysis symbols, so you don’t have to waste time searching for or manually creating custom fault tree analysis symbols. This built-in library covers all essential fault tree events and gates, from basic events and intermediate events to logic gates like AND, OR, and XOR, along with transfer symbols for managing complex diagrams. You can quickly drag and drop the fault tree analysis symbols onto your workspace and connect them to visualize the flow of system failures in a structured, easy-to-understand manner.

4. Templates for Faster Setup

Creately offers a range of pre-designed FTA templates to help you get started quickly. These templates are customizable and can serve as a base for your analysis, saving you time during the initial setup. Whether you’re analyzing a specific type of system or using a standard fault tree structure, Creately’s templates can accelerate the process and ensure consistency across your projects.

5. Cloud-Based Accessibility

Creately is cloud-based, which means you can access your fault tree diagrams from anywhere, at any time. Whether you’re working from the office, home, or on-site, you can quickly pull up your diagrams, make real-time updates, and share them with others. This accessibility ensures that your team remains connected and productive, even when working in different locations.

Final Thoughts: Mastering Fault Tree Analysis with the Right Tools

Fault Tree Analysis (FTA) is an essential tool for understanding system reliability, identifying potential failures, and mitigating risks. By utilizing fault tree analysis symbols effectively, you can transform complex systems into clear, actionable diagrams that provide valuable insights into potential failure modes and their causes.

Throughout this guide, we’ve explored the different types of fault tree analysis symbols, including logic gates, event types, transfer symbols, and their roles in structuring and analyzing fault trees. Understanding these fault tree analysis symbols is critical to performing thorough FTA, ensuring that engineers and safety professionals can make informed decisions to enhance system performance and reliability.

Additionally, adopting best practices for diagramming, such as maintaining clarity, consistency, and accuracy, will improve the overall effectiveness of your FTA process. By using the right tools, such as Creately, you can streamline the creation of fault tree diagrams, foster real-time collaboration, and integrate your analysis into larger risk assessments and reliability studies.

With the right understanding of fault tree analysis symbols and the right tools at your disposal, you can enhance your ability to predict and prevent system failures, ensuring a safer, more reliable operation for any system, process, or industry.

FAQs About Fault Tree Analysis Symbols

What are fault tree analysis symbols and why are they important?

How do logic gates function in fault tree analysis symbols?

What is the difference between basic events and undeveloped events in fault tree analysis symbols?

How do transfer symbols enhance fault tree analysis?

Why should I use specialized tools like Creately for designing fault tree analysis symbols?

Resources: Beresh, R., Ciufo, J. and Anders, G. (2008). Basic fault tree analysis for use in protection reliability. International Journal of Reliability and Safety, 2(1/2), p.64. doi:www.doi.org/10.1504/ijrs.2008.020773.

Kabir, S. (2017). An overview of fault tree analysis and its application in model based dependability analysis. Expert Systems with Applications, [online] 77, pp.114–135. doi:www.doi.org/10.1016/j.eswa.2017.01.058.

Ruijters, E. and Stoelinga, M. (2015). Fault tree analysis: A survey of the state-of-the-art in modeling, analysis and tools. Computer Science Review, [online] 15-16(1574-0137), pp.29–62. doi:https://doi.org/10.1016/j.cosrev.2015.03.001.